TMDS协议

1 概述

1.1 连接结构

center">c="http://hi.csdn.net/attachment/201111/9/0_1320858089TMdu.gif" />

center">图1 TMDS连接结构

数据流中包含了像素和控制数据c;发送器在任何给定的输入时钟周期c;到底是编码像素数据还是控制数据取决于数据使能信号DEc;DE有效时c;指示像素数据要被发送c;注意c;当发送像素数据的时候c;忽略控制数据c;反之c;发送控制数据的时候c;忽略像素数据。在接收端c;恢复的像素(控制)数据仅在DE有效(无效)时才传输。

我们把DE有效期间c;成为像素数据有效期间c;就是说这段时间发送的是有效像素数据。DE无效期间c;成为发送空间隙期间c;这段时间发送的数据不包括有效像素数据c;仅仅是控制信号。

发送端有3个一模一样的编码器c;每个编码器的输入是2个控制信号和8bit的像素数据。依照DE的状态c;编码器将按照两个控制信号的状态或8bit像素数据产生10bit的TMDS字符。每个解码器输出是一个连续的串行TMDS字符流。

1.2 时钟

TMDS时钟通道的时钟频率就是字符速率c;接收器利用这个时钟c;产生用于串行流接收的位采样时钟c;由于要求能容忍信号畸变c;所以期望每个数据通道的位采样时钟的相位能够单独调整。

1.3 同步

TMDS接收器必须能在串行数据流中确定字符边界。一旦所有的数据通道字符边界被建立c;我们就说c;此时接收器与数据流同步并可以从数据通道中接收TMDS字符加以译码。TMDS数据流提供周期性的提示用于解码同步。

用来作为像素数据的TMDS字符包含5个或更少的跳变c;而用来作为控制数据的TMDS字符包含7个或更多的跳变。在空期间传送的多跳变内容形成解码端的字符边界的基础c;这些字符在串行数据流中个体不是独一无二c;但它们足够相似c;使得c;在发送空间隙期间c;解码器它们可以唯一地检测出它们连续的存在。

1.4 编码

TMDS数据通道传送的是一个连续的10bit TMDS字符流c;在空期间c;传送4个有显著特征的字符c;它们直接对应编码器的2个控制信号的4个可能的状态。在数据有效期间c;10bit的字符包含8bit的像素数据c;编码的字符提供近似的DC平衡c;并最少化数据流的跳变次数c;对有效像素数据的编码处理可以认为有两个阶段:第一个阶段是依据输入的8bit像素数据产生跳变最少的9bit代码字;第二阶段是产生一个10bit的代码字c;最终的TMDS字符c;将维持发送字符总体的DC平衡。

编码器在第一个阶段产生的9bit代码字由“8bit” + “1bit”组成c;“8bit”反映输入的8bit数据位的跳变c;“1bit”表示用来描述跳变的两个方法中哪一个被使用c;无论哪种方法c;输出的最低位都会与输入的最低位相匹配。用一个建立的初值c;输出字的余下7bit的产生是按照顺序将输入的每一位与前一导出的位进行XOR或NOR(XNOR)。使用XOR还是XNOR要看哪个方法使得编码结果包含最少的跳变c;代码字的第9位用来表示导出输出代码是使用XOR还是XNORc;这9bit代码字的解码方法很简单c;就是相邻位的XOR或XNOR操作。从解码输入到解码器输出最低位不改变。

在有效数据期间c;编码器执行使传输的数据流维持近似的DC平衡处理c;这是通过选择性地反转第一阶段产生的9bit代码中的8bit数据位来实现的c;第10bit被加到代码字上c;表示是否进行了反转处理c;编码器是基于跟踪发送流中1和0个数的不一致以及当前代码字1和0的数目来确定什么时候反转下一个TMDS字符。如果太多的1被发送c;且输入包含的1多于0c;则代码字反转c;这个发送端的动态编码决定在接收端可以很简单地解码出来c;方法是以TMDS字符的第10bit决定是否对输入代码进行反转。

1.5 双连接结构

TMDS连接结构的数据通道数目的选择主要基于下面两点考虑:一是视频数据要求的带宽c;二是对每个像素的R、G、B分量c;每个分量对应于一个通道c;从而使得逻辑简单。在这里双TMDS链路等同于使用6个数据通道共享一个时钟通道c;这样使得接口带宽加倍。对于这个配置c;第一个数据链路传输奇数像素点c;而第二个数据链路传输偶数像素点。每一行的第一个像素是奇数像素c;即为像素1。

2 编码

2.1 通道映射

单链路TMDS发送器由三个相同的编码器组成c;如图2c;2个控制信号和8bit像素数据映射到每个编码器c;双链路发送器增加了三个数据通道c;如图3c;双链路配置在第一个链路上发送每行的奇像素c;在第二个链路上发送每行的偶像素c;每一行的第一个像素是奇数像素c;即为像素1。

center">c="http://hi.csdn.net/attachment/201111/9/0_1320858126PfhB.gif" />

center">图2 单链路TMDS通道映射

除了行同步HS和场同步VS外c;其它控制信号的作用并没有定义c;在发送器的输入端c;控制信号CTL1、CLT2、CTL3必须保持逻辑低电平c;推荐CTL0也保持逻辑低电平c;由于历史原因c;某些发送器芯片可以通过CTL0传递一个控制信号c;如果这么做c;仅需要满足一个条件:这个信号发生在单像素输入时钟的奇边缘或偶边缘。当链路有效的时候c;在奇偶之间一定不要来回切换。

center">c="http://hi.csdn.net/attachment/201111/9/0_13208581472Dm8.gif" />

center">图3 双链路TMDS通道映射

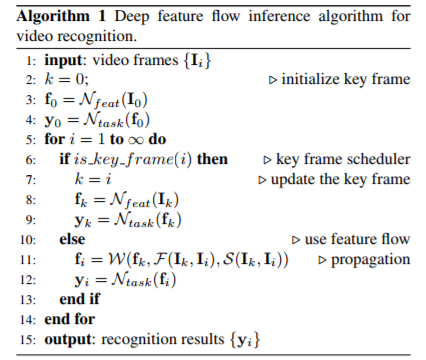

2.2 编码class="tags" href="/tags/SuanFa.html" title=算法>算法

TMDS编码class="tags" href="/tags/SuanFa.html" title=算法>算法c;如图5所示c;在空间隙c;编码器产生4个独一无二的字符c;以及在有效的数据期间c;产生460个独一无二的10bit字符中的一个c;在链路上c;除此以外的其它10bit字符是保留的c;编码器不会产生这些字符。

| D, C0, C1, DE | |

| Cnt | 这是个寄存器c;用来跟踪数据流的不一致c;正值表示发送的1的个数超过的数目c;负数表示发送的0的个数超过的数目。表达式cnt{t-1}表示相对于输入数据前一个集的前一个不一致值。表达式cnt{t}表示相对于输入数据当前集的新的不一致设置。 |

| q_out | 这些10bit数是编码器产生的。 |

| N1{x} | 这个操作符返回参数x中的1的个数 |

| N0{x} | 这个操作符返回参数x中的0的个数 |

center">c="http://hi.csdn.net/attachment/201111/9/0_1320858168cOXC.gif" />

center">图5 TMDS编码class="tags" href="/tags/SuanFa.html" title=算法>算法

2.3 串行化

由编码器形成的TMDS字符流转换为串行数据c;用于在TMDS数据通道上发送c;低位在前先发送。

3 解码

3.1 时钟恢复

TMDS接收器必须有能力相位锁定与发送时钟c;发送时钟的时钟频率范围是25MHz到接收器的最大允许频率c;对输入时钟的相位锁定必须发生在从输入时钟满足规定起100ms之前。

3.2 数据同步

接收器要求在任何大于128字符长度的空间隙期间c;建立与数据流的同步。

在同步检测之前c;和在丢失同步期间c;接收器不应该更新接收到的数据流信号。

3.3 解码class="tags" href="/tags/SuanFa.html" title=算法>算法

center">c="http://hi.csdn.net/attachment/201111/9/0_1320858189ghle.gif" />

center">图6 TMDS解码class="tags" href="/tags/SuanFa.html" title=算法>算法

3.4 通道映射

如图2和图3

3.5 错误处理

TMDS链路不要求错误处理能力。

4 链路定时要求

center">c="http://hi.csdn.net/attachment/201111/9/0_132085822109RQ.gif" />

center">图7 TMDS链路定时

| 符号 | 描述 | 值 | 单位 |

| tB | 最小空间隙c;为了在接收端确保字符边界的恢复c;要求有这个最短的空间隙c;空间隙至少每50mS(20Hz)出现一次。 | 128 | Tpixel |

| tE | 最大编码/并转串电路管线延迟 | 64 | Tpixel |

| tR | 64 | Tpixel |